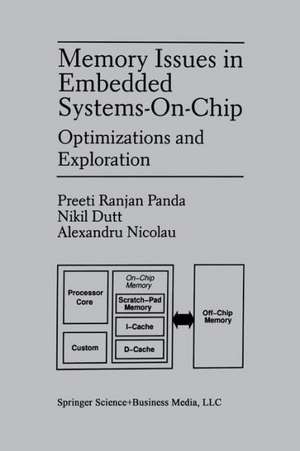

Memory Issues in Embedded Systems-on-Chip: Optimizations and Exploration

Autor Preeti Ranjan Panda, Nikil D. Dutt, Alexandru Nicolauen Limba Engleză Paperback – 5 noi 2012

First, it is designed for researchers and graduate students who wish to understand the research issues involved in memory system optimization and exploration for embedded systems-on-chip.

Second, it is intended for designers of embedded systems who are migrating from a traditional micro-controllers centered, board-based design methodology to newer design methodologies using IP blocks for processor-core-based embedded systems-on-chip.

Also, since Memory Issues in Embedded Systems-on-Chip: Optimization and Explorations illustrates a methodology for optimizing and exploring the memory configuration of embedded systems-on-chip, it is intended for managers and system designers who may be interested in the emerging capabilities of embedded systems-on-chip design methodologies for memory-intensive applications.

| Toate formatele și edițiile | Preț | Express |

|---|---|---|

| Paperback (1) | 636.30 lei 6-8 săpt. | |

| Springer Us – 5 noi 2012 | 636.30 lei 6-8 săpt. | |

| Hardback (1) | 640.88 lei 6-8 săpt. | |

| Springer Us – 31 oct 1998 | 640.88 lei 6-8 săpt. |

Preț: 636.30 lei

Preț vechi: 748.59 lei

-15% Nou

Puncte Express: 954

Preț estimativ în valută:

121.77€ • 126.36$ • 101.78£

121.77€ • 126.36$ • 101.78£

Carte tipărită la comandă

Livrare economică 15-29 martie

Preluare comenzi: 021 569.72.76

Specificații

ISBN-13: 9781461373230

ISBN-10: 1461373239

Pagini: 212

Ilustrații: XIX, 188 p.

Dimensiuni: 155 x 235 x 11 mm

Greutate: 0.3 kg

Ediția:Softcover reprint of the original 1st ed. 1999

Editura: Springer Us

Colecția Springer

Locul publicării:New York, NY, United States

ISBN-10: 1461373239

Pagini: 212

Ilustrații: XIX, 188 p.

Dimensiuni: 155 x 235 x 11 mm

Greutate: 0.3 kg

Ediția:Softcover reprint of the original 1st ed. 1999

Editura: Springer Us

Colecția Springer

Locul publicării:New York, NY, United States

Public țintă

ResearchCuprins

1. Introduction.- 1.1 Embedded Systems-on-Chip Design.- 1.2 Synthesis, Compilation and Architecture for Embedded SOC.- 1.3 Embedded System Architecture.- 1.4 Organization of the Book.- 2. Background.- 2.1 Introduction.- 2.2 Exploiting Memory Hierarchy.- 2.3 Memory Issues in Embedded Systems.- 2.4 In this book.- 3. Off-Chip Memory Access Optimizations.- 3.1 Incorporating Off-chip Memory Accesses into Synthesis.- 3.2 Power Optimizations in Memory Accesses.- 3.3 Summary.- 4. Data Organization: The Processor Core/Cache Interface.- 4.1 Introduction.- 4.2 Memory Data Organization.- 4.3 Data Alignment for Loop Blocking.- 4.4 Summary.- 5. On-Chip vs. Off-Chip Memory: Utilizing Scratch-Pad Memory.- 5.1 Scratch-Pad Memory.- 5.2 Problem Description.- 5.3 The Partitioning Strategy.- 5.4 Context Switching.- 5.5 Generalized Memory Hierarchy.- 5.6 Experiments.- 5.7 Summary.- 6. Memory Architecture Exploration.- 6.1 Motivation.- 6.2 Illustrative Example.- 6.3 Exploration Strategy.- 6.4 Memory Performance Estimation.- 6.5 Experiments.- 6.6 Summary.- 7. Case Study: MPEG Decoder.- 7.1 Overview of MPEG Decoder.- 7.2 Memory Exploration of Sample Routines.- 7.3 Memory Exploration of MPEG Decoder.- 7.4 Summary.- 8. Conclusions.- 8.1 Extending this Work.- 8.2 Future Directions.- References.