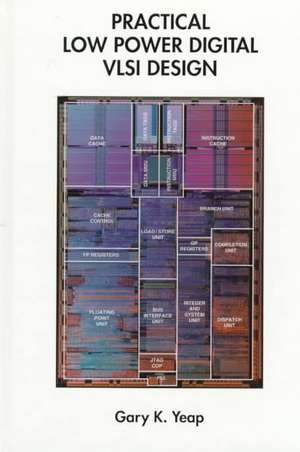

Practical Low Power Digital VLSI Design

Autor Gary K. Yeapen Limba Engleză Hardback – 31 aug 1997

Practical Low Power Digital VLSI Design considers a wide range of design abstraction levels spanning circuit, logic, architecture and system. Substantial basic knowledge is provided for qualitative and quantitative analysis at the different design abstraction levels. Low power techniques are presented at the circuit, logic, architecture and system levels. Special techniques that are specific to some key areas of digital chip design are discussed as well as some of the low power techniques that are just appearing on the horizon.

Practical Low Power Digital VLSI Design will be of benefit to VLSI design engineers and students who have a fundamental knowledge of CMOS digital design.

| Toate formatele și edițiile | Preț | Express |

|---|---|---|

| Paperback (1) | 1104.88 lei 6-8 săpt. | |

| Springer Us – 21 oct 2012 | 1104.88 lei 6-8 săpt. | |

| Hardback (1) | 1108.99 lei 6-8 săpt. | |

| Springer Us – 31 aug 1997 | 1108.99 lei 6-8 săpt. |

Preț: 1108.99 lei

Preț vechi: 1352.42 lei

-18% Nou

Puncte Express: 1663

Preț estimativ în valută:

212.21€ • 226.92$ • 176.93£

212.21€ • 226.92$ • 176.93£

Carte tipărită la comandă

Livrare economică 18 aprilie-02 mai

Preluare comenzi: 021 569.72.76

Specificații

ISBN-13: 9780792380092

ISBN-10: 0792380096

Pagini: 212

Ilustrații: XV, 212 p.

Dimensiuni: 155 x 235 x 20 mm

Greutate: 0.45 kg

Ediția:1998

Editura: Springer Us

Colecția Springer

Locul publicării:New York, NY, United States

ISBN-10: 0792380096

Pagini: 212

Ilustrații: XV, 212 p.

Dimensiuni: 155 x 235 x 20 mm

Greutate: 0.45 kg

Ediția:1998

Editura: Springer Us

Colecția Springer

Locul publicării:New York, NY, United States

Public țintă

ResearchCuprins

1 Introduction.- 1.1 Needs for Low Power VLSI Chips.- 1.2 Charging and Discharging Capacitance.- 1.3 Short-circuit Current in CMOS Circuit.- 1.4 CMOS Leakage Current.- 1.5 Static Current.- 1.6 Basic Principles of Low Power Design.- 1.7 Low Power Figure of Merits.- 2 Simulation Power Analysis.- 2.1 SPICE Circuit Simulation.- 2.2 Discrete Transistor Modeling and Analysis.- 2.3 Gate-level Logic Simulation.- 2.4 Architecture-level Analysis.- 2.5 Data Correlation Analysis in DSP Systems.- 2.6 Monte Carlo Simulation.- 3 Probabilistic Power Analysis.- 3.1 Random Logic Signals.- 3.2 Probability and Frequency.- 3.3 Probabilistic Power Analysis Techniques.- 3.4 Signal Entropy.- 4 Circuit.- 4.1 Transistor and Gate Sizing.- 4.2 Equivalent Pin Ordering.- 4.3 Network Restructuring and Reorganization.- 4.4 Special Latches and Flip-flops.- 4.5 Low Power Digital Cell Library.- 4.6 Adjustable Device Threshold Voltage.- 5 Logic.- 5.1 Gate Reorganization.- 5.2 Signal Gating.- 5.3 Logic Encoding.- 5.4 State Machine Encoding.- 5.5 Precomputation Logic.- 6 Special Techniques.- 6.1 Power Reduction in Clock Networks.- 6.2 CMOS Floating Node.- 6.3 Low Power Bus.- 6.4 Delay Balancing.- 6.5 Low Power Techniques for SRAM.- 7 Architecture and System.- 7.1 Power and Performance Management.- 7.2 Switching Activity Reduction.- 7.3 Parallel Architecture with Voltage Reduction.- 7.4 Flow Graph Transformation.- 8 Advanced Techniques.- 8.1 Adiabatic Computation.- 8.2 Pass Transistor Logic Synthesis.- 8.3 Asynchronous Circuits.