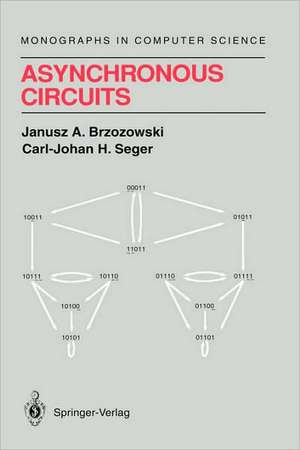

Asynchronous Circuits: Monographs in Computer Science

Autor Janusz A. Brzozowski Cuvânt înainte de C.E. Molnar Autor Carl-Johan H. Segeren Limba Engleză Hardback – 24 feb 1995

This book provides a comprehensive theory of asynchronous circuits, including modelling, analysis, simulation, specification, verification, and an introduction to their design. It is based on courses given to graduate students and will be suitable for computer scientists and engineers involved in the research and development of asynchronous designs.

| Toate formatele și edițiile | Preț | Express |

|---|---|---|

| Paperback (1) | 950.52 lei 6-8 săpt. | |

| Springer – 11 noi 2011 | 950.52 lei 6-8 săpt. | |

| Hardback (1) | 956.81 lei 6-8 săpt. | |

| Springer – 24 feb 1995 | 956.81 lei 6-8 săpt. |

Din seria Monographs in Computer Science

- 20%

Preț: 1322.33 lei

Preț: 1322.33 lei - 20%

Preț: 511.92 lei

Preț: 511.92 lei - 20%

Preț: 1285.31 lei

Preț: 1285.31 lei - 20%

Preț: 333.22 lei

Preț: 333.22 lei - 20%

Preț: 328.60 lei

Preț: 328.60 lei - 15%

Preț: 646.94 lei

Preț: 646.94 lei - 20%

Preț: 357.48 lei

Preț: 357.48 lei - 20%

Preț: 339.47 lei

Preț: 339.47 lei - 20%

Preț: 653.21 lei

Preț: 653.21 lei - 20%

Preț: 329.44 lei

Preț: 329.44 lei - 20%

Preț: 993.74 lei

Preț: 993.74 lei - 20%

Preț: 992.26 lei

Preț: 992.26 lei - 20%

Preț: 1630.95 lei

Preț: 1630.95 lei - 20%

Preț: 656.03 lei

Preț: 656.03 lei - 20%

Preț: 650.08 lei

Preț: 650.08 lei - 20%

Preț: 328.09 lei

Preț: 328.09 lei - 20%

Preț: 641.16 lei

Preț: 641.16 lei - 20%

Preț: 334.38 lei

Preț: 334.38 lei - 18%

Preț: 737.74 lei

Preț: 737.74 lei - 20%

Preț: 642.19 lei

Preț: 642.19 lei - 20%

Preț: 641.99 lei

Preț: 641.99 lei - 20%

Preț: 345.59 lei

Preț: 345.59 lei - 20%

Preț: 711.29 lei

Preț: 711.29 lei - 20%

Preț: 1001.16 lei

Preț: 1001.16 lei - 20%

Preț: 661.47 lei

Preț: 661.47 lei - 20%

Preț: 343.62 lei

Preț: 343.62 lei - 20%

Preț: 644.81 lei

Preț: 644.81 lei - 15%

Preț: 505.30 lei

Preț: 505.30 lei - 20%

Preț: 640.69 lei

Preț: 640.69 lei -

Preț: 396.78 lei

Preț: 396.78 lei - 20%

Preț: 592.68 lei

Preț: 592.68 lei - 20%

Preț: 329.44 lei

Preț: 329.44 lei -

Preț: 383.33 lei

Preț: 383.33 lei - 20%

Preț: 349.40 lei

Preț: 349.40 lei - 20%

Preț: 832.40 lei

Preț: 832.40 lei - 20%

Preț: 993.42 lei

Preț: 993.42 lei - 15%

Preț: 578.87 lei

Preț: 578.87 lei - 20%

Preț: 337.85 lei

Preț: 337.85 lei - 20%

Preț: 988.16 lei

Preț: 988.16 lei - 20%

Preț: 996.56 lei

Preț: 996.56 lei - 20%

Preț: 1293.37 lei

Preț: 1293.37 lei - 20%

Preț: 1452.94 lei

Preț: 1452.94 lei

Preț: 956.81 lei

Preț vechi: 1166.84 lei

-18% Nou

Puncte Express: 1435

Preț estimativ în valută:

183.11€ • 190.46$ • 151.17£

183.11€ • 190.46$ • 151.17£

Carte tipărită la comandă

Livrare economică 14-28 aprilie

Preluare comenzi: 021 569.72.76

Specificații

ISBN-13: 9780387944203

ISBN-10: 0387944206

Pagini: 404

Ilustrații: XVI, 404 p.

Dimensiuni: 156 x 234 x 24 mm

Greutate: 0.77 kg

Ediția:1995

Editura: Springer

Colecția Springer

Seria Monographs in Computer Science

Locul publicării:New York, NY, United States

ISBN-10: 0387944206

Pagini: 404

Ilustrații: XVI, 404 p.

Dimensiuni: 156 x 234 x 24 mm

Greutate: 0.77 kg

Ediția:1995

Editura: Springer

Colecția Springer

Seria Monographs in Computer Science

Locul publicării:New York, NY, United States

Public țintă

ResearchCuprins

1 Introductory Examples.- 1.1 Logic Gates.- 1.2 Performance Estimation.- 1.3 RS Flip-Flop.- 1.4 Dynamic CMOS Logic.- 1.5 Divide-by-2 Counter.- 1.6 Summary.- 2 Mathematical Background.- 2.1 Sets and Relations.- 2.2 Boolean Algebra.- 2.3 Ternary Algebra.- 2.4 Directed Graphs.- 3 Delay Models.- 3.1 Environment Modes.- 3.2 Gates with Delays.- 3.3 Ideal Delays.- 3.4 Inertial Delays.- 4 Gate Circuits.- 4.1 Properties of Gates.- 4.2 Classes of Gate Circuits.- 4.3 The Circuit Graph.- 4.4 Network Models.- 4.5 Models of More Complex Gates.- 5 CMOS Transistor Circuits.- 5.1 CMOS Cells.- 5.2 Combinational CMOS Circuits.- 5.3 General CMOS Circuits.- 5.4 Node Excitation Functions.- 5.5 Path Strength Models.- 5.6 Capacitance Effects.- 5.7 Network Model of CMOS Circuits.- 6 Up-Bounded-Delay Race Models.- 6.1 The General Multiple-Winner Model.- 6.2 GMW Analysis and UIN Delays.- 6.3 The Outcome in GMW Analysis.- 6.4 Stable States and Feedback-State Networks.- 6.5 GMW Analysis and Network Models.- 6.6 The Extended GMW Model.- 6.7 Single-Winner Race Models.- 6.8 Up-Bounded Ideal Delays.- 6.9 Proofs.- 7 Ternary Simulation.- 7.1 Introductory Examples.- 7.2 Algorithm A.- 7.3 Algorithm B.- 7.4 Feedback-Delay Models.- 7.5 Hazards.- 7.6 Ternary Simulation and the GSW Model.- 7.7 Ternary Simulation and the XMW Model.- 7.8 Proofs of Main Results.- 8 Bi-Bounded Delay Models.- 8.1 Discrete Binary Models.- 8.2 Continuous Binary Model.- 8.3 Algorithms for Continuous Binary Analysis.- 8.4 Continuous Ternary Model.- 8.5 Discrete Ternary Model.- 9 Complexity of Race Analysis.- 9.1 Stable-State Reachability.- 9.2 Limited Reachability.- 10 Regular Languages and Finite Automata.- 10.1 Regular Languages.- 10.2 Regular Expressions.- 10.3 Quotient Equations.- 10.4 Finite Automata.- 10.5 Equivalence and Reduction of Automata.- 10.6 Nondeterministic Automata.- 10.7 Expression Automata.- 11 Behaviors and Realizations.- 11.1 Motivation.- 11.2 Behaviors.- 11.3 Projections of Implementations to Specifications.- 11.4 Relevant Words.- 11.5 Proper Behaviors.- 11.6 Realization.- 11.7 Behavior Schemas.- 11.8 Concluding Remarks.- 12 Types of Behaviors.- 12.1 Introductory Examples.- 12.2 Fundamental-Mode Specifications.- 12.3 Fundamental-Mode Network Behaviors.- 12.4 Direct Behaviors.- 12.5 Serial Behaviors.- 13 Limitations of Up-Bounded Delay Models.- 13.1 Delay-Insensitivity in Fundamental Mode.- 13.2 Composite Functions.- 13.3 Main Theorem for Fundamental Mode.- 13.4 Delay-Insensitivity in Input/Output Mode.- 13.5 Concluding Remarks.- 14 Symbolic Analysis.- 14.1 Representing Boolean Functions.- 14.2 Symbolic Representations.- 14.3 Deriving Symbolic Behaviors.- 14.4 Symbolic Race Analysis.- 14.5 Symbolic Verification of Realization.- 14.6 Symbolic Model Checking.- 15 Design of Asynchronous Circuits.- 15.1 Introduction.- 15.2 Fundamental-Mode Huffman Circuits.- 15.3 Hollaar Circuits.- 15.4 Burst-Mode Circuits.- 15.5 Module Synthesis Using I-Nets.- 15.6 Signal Transition Graphs.- 15.7 Change Diagrams.- 15.8 Protocols in DI Circuits.- 15.9 Ebergen’s Trace Theory Method.- 15.10 Compilation of Communicating Processes.- 15.11 Handshake Circuits.- 15.12 Module-Based Compilation Systems.- 15.13 DCVSL and Interconnection Modules.- 15.14 Micropipelines.- 15.15 Concluding Remarks.- List of Figures.- List of Tables.- List of Mathematical Concepts.