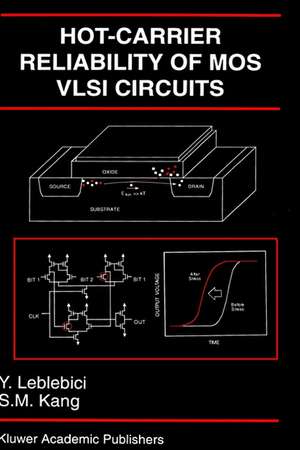

Hot-Carrier Reliability of MOS VLSI Circuits: The Springer International Series in Engineering and Computer Science, cartea 227

Autor Yusuf Leblebici, Sung-Mo (Steve) Kangen Limba Engleză Hardback – 30 iun 1993

| Toate formatele și edițiile | Preț | Express |

|---|---|---|

| Paperback (1) | 1213.97 lei 6-8 săpt. | |

| Springer Us – 27 sep 2012 | 1213.97 lei 6-8 săpt. | |

| Hardback (1) | 1219.94 lei 6-8 săpt. | |

| Springer Us – 30 iun 1993 | 1219.94 lei 6-8 săpt. |

Din seria The Springer International Series in Engineering and Computer Science

- 24%

Preț: 1041.98 lei

Preț: 1041.98 lei - 20%

Preț: 643.50 lei

Preț: 643.50 lei - 18%

Preț: 1225.62 lei

Preț: 1225.62 lei - 18%

Preț: 965.02 lei

Preț: 965.02 lei - 20%

Preț: 646.12 lei

Preț: 646.12 lei - 18%

Preț: 948.79 lei

Preț: 948.79 lei - 20%

Preț: 646.62 lei

Preț: 646.62 lei - 15%

Preț: 637.46 lei

Preț: 637.46 lei - 20%

Preț: 643.83 lei

Preț: 643.83 lei - 18%

Preț: 949.23 lei

Preț: 949.23 lei - 20%

Preț: 644.48 lei

Preț: 644.48 lei - 20%

Preț: 994.92 lei

Preț: 994.92 lei - 20%

Preț: 645.97 lei

Preț: 645.97 lei - 18%

Preț: 946.87 lei

Preț: 946.87 lei - 20%

Preț: 995.57 lei

Preț: 995.57 lei - 18%

Preț: 956.99 lei

Preț: 956.99 lei - 20%

Preț: 644.98 lei

Preț: 644.98 lei - 15%

Preț: 649.54 lei

Preț: 649.54 lei - 18%

Preț: 950.21 lei

Preț: 950.21 lei - 18%

Preț: 1221.38 lei

Preț: 1221.38 lei - 18%

Preț: 957.62 lei

Preț: 957.62 lei - 15%

Preț: 643.99 lei

Preț: 643.99 lei - 18%

Preț: 948.47 lei

Preț: 948.47 lei - 18%

Preț: 947.35 lei

Preț: 947.35 lei - 20%

Preț: 1284.65 lei

Preț: 1284.65 lei - 20%

Preț: 1628.31 lei

Preț: 1628.31 lei - 20%

Preț: 1285.78 lei

Preț: 1285.78 lei

Preț: 1219.94 lei

Preț vechi: 1487.73 lei

-18% Nou

Puncte Express: 1830

Preț estimativ în valută:

233.47€ • 242.84$ • 192.74£

233.47€ • 242.84$ • 192.74£

Carte tipărită la comandă

Livrare economică 15-29 aprilie

Preluare comenzi: 021 569.72.76

Specificații

ISBN-13: 9780792393528

ISBN-10: 079239352X

Pagini: 212

Ilustrații: XVII, 212 p.

Dimensiuni: 155 x 235 x 14 mm

Greutate: 0.51 kg

Ediția:1993

Editura: Springer Us

Colecția Springer

Seria The Springer International Series in Engineering and Computer Science

Locul publicării:New York, NY, United States

ISBN-10: 079239352X

Pagini: 212

Ilustrații: XVII, 212 p.

Dimensiuni: 155 x 235 x 14 mm

Greutate: 0.51 kg

Ediția:1993

Editura: Springer Us

Colecția Springer

Seria The Springer International Series in Engineering and Computer Science

Locul publicării:New York, NY, United States

Public țintă

ResearchCuprins

1. Introduction.- 1.1. The Concept of IC Reliability.- 1.2. Design-for-Reliability.- 1.3. VLSI Reliability Problems.- 1.4. Gradual Degradation versus Catastrophic Failures.- 1.5. Hot-Carrier Effects.- 1.6. Overview of the Book.- References.- 2. Oxide Degradation Mechanisms in Mos Transistors.- 2.1. Introduction.- 2.2. MOS Transistor: A Qualitative View.- 2.3. The Nature of Gate Oxide Damage in MOSFETs.- 2.4. Injection of Hot Carriers into Gate Oxide.- 2.5. Oxide Traps and Charge Trapping.- 2.6. Interface Trap Generation.- 2.7. Bias Dependence of Degradation Mechanisms.- 2.8. Degradation under Dynamic Operating Conditions.- 2.9. Effects of Hot-Carrier Damage on Device Characteristics.- 2.10. Hot-Carrier Induced Degradation of pMOS Transistors.- References.- 3.Modeling of Degradation Mechanisms.- 3.1. Preliminary Remarks.- 3.2. Quasi-Elastic Scattering Current Model.- 3.3. Charge (Electron) Trapping Model.- 3.4. Impact Ionization Current Model.- 3.5. Interface Trap Generation Model.- 3.6. Trap Generation under Dynamic Operating Conditions.- References.- 4. Modeling of Damaged Mosfets.- 4.1. Introduction.- 4.2. Representation of Hot-Carrier Induced Oxide Damage.- 4.3. Two-Dimensional Modeling of Damaged MOSFETs.- 4.4. Empirical One-Dimensional Modeling.- 4.5. An Analytical Damaged MOSFET Model.- 4.6. Consideration of Channel Velocity Limitations.- 4.7. Pseudo Two-Dimensional Modeling of Damaged MOSFETs.- 4.8. Table-Based Modeling Approaches.- References.- 5. Transistor-Level Simulation for Circuit Reliability.- 5.1. Introduction.- 5.2. Review of Circuit Reliability Simulation Tools.- 5.3. Circuit Reliability Simulation Using iSMILE: A Case Study.- 5.4. Circuit Simulation Examples.- 5.5. Evaluation of the Simulation Algorithm.- 5.6. Identification of Critical Devices.- References.- 6. Fast Timing Simulation for Circuit Reliability.- 6.1. Introduction.- 6.2. ILLIADS-R: A Fast Timing and Reliability Simulator.- 6.3. Fast Dynamic Reliability Simulation.- 6.4. Circuit Simulation Examples with ILLIADS-R.- 6.5. iDSIM2: Hierarchical Circuit Reliability Simulation.- References.- 7. Macromodeling of Hot-Carrier Induced Degradation in Mos Circuits.- 7.1. Introduction.- 7.2. Macromodel Development: Starting Assumptions.- 7.3. Degradation Macromodel for CMOS Inverters.- 7.4. Degradation Macromodel for nMOS Pass Gates.- 7.5. Application of the Macromodel to Inverter Chain Circuits.- 7.6. Application of the Macromodel to CMOS Logic Circuits.- References.- 8. Circuit Design for Reliability.- 8.1. Introduction.- 8.2. Device-Level Measures.- 8.3. Circuit-Level Measures.- 8.4. Rule-Based Diagnosis of Circuit Reliability.- References.