Test Resource Partitioning for System-on-a-Chip: Frontiers in Electronic Testing, cartea 20

Autor Vikram Iyengar, Anshuman Chandraen Limba Engleză Hardback – 30 iun 2002

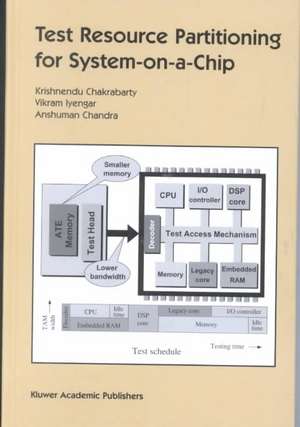

SOC integrated circuits composed of embedded cores are now commonplace. Nevertheless, There remain several roadblocks to rapid and efficient system integration. Test development is seen as a major bottleneck in SOC design, and test challenges are a major contributor to the widening gap between design capability and manufacturing capacity. Testing SOCs is especially challenging in the absence of standardized test structures, test automation tools, and test protocols.

Test Resource Partitioning for System-on-a-Chip responds to a pressing need for a structured methodology for SOC test automation. It presents new techniques for the partitioning and optimization of the three major SOC test resources: test hardware, testing time and test data volume.

Test Resource Partitioning for System-on-a-Chip paves the way for a powerful integrated framework to automate the test flow for a large number of cores in an SOC in a plug-and-play fashion. The framework presented allows the system integrator to reduce test cost and meet short time-to-market requirements.

| Toate formatele și edițiile | Preț | Express |

|---|---|---|

| Paperback (1) | 638.11 lei 43-57 zile | |

| Springer Us – 7 noi 2012 | 638.11 lei 43-57 zile | |

| Hardback (1) | 644.49 lei 43-57 zile | |

| Springer Us – 30 iun 2002 | 644.49 lei 43-57 zile |

Din seria Frontiers in Electronic Testing

- 15%

Preț: 639.25 lei

Preț: 639.25 lei - 18%

Preț: 1110.24 lei

Preț: 1110.24 lei - 18%

Preț: 948.47 lei

Preț: 948.47 lei - 18%

Preț: 946.55 lei

Preț: 946.55 lei - 18%

Preț: 952.72 lei

Preț: 952.72 lei - 18%

Preț: 944.82 lei

Preț: 944.82 lei - 18%

Preț: 808.75 lei

Preț: 808.75 lei - 18%

Preț: 945.79 lei

Preț: 945.79 lei - 18%

Preț: 1226.24 lei

Preț: 1226.24 lei - 15%

Preț: 649.87 lei

Preț: 649.87 lei - 18%

Preț: 943.07 lei

Preț: 943.07 lei - 15%

Preț: 642.51 lei

Preț: 642.51 lei - 18%

Preț: 948.61 lei

Preț: 948.61 lei - 18%

Preț: 953.65 lei

Preț: 953.65 lei - 15%

Preț: 645.14 lei

Preț: 645.14 lei - 15%

Preț: 644.30 lei

Preț: 644.30 lei - 18%

Preț: 951.29 lei

Preț: 951.29 lei - 20%

Preț: 990.30 lei

Preț: 990.30 lei - 18%

Preț: 968.03 lei

Preț: 968.03 lei - 18%

Preț: 947.35 lei

Preț: 947.35 lei - 15%

Preț: 642.51 lei

Preț: 642.51 lei - 15%

Preț: 646.11 lei

Preț: 646.11 lei - 15%

Preț: 641.85 lei

Preț: 641.85 lei - 18%

Preț: 950.96 lei

Preț: 950.96 lei

Preț: 644.49 lei

Preț vechi: 758.23 lei

-15% Nou

Puncte Express: 967

Preț estimativ în valută:

123.36€ • 134.04$ • 103.69£

123.36€ • 134.04$ • 103.69£

Carte tipărită la comandă

Livrare economică 21 aprilie-05 mai

Preluare comenzi: 021 569.72.76

Specificații

ISBN-13: 9781402071195

ISBN-10: 1402071191

Pagini: 232

Ilustrații: XII, 232 p.

Dimensiuni: 155 x 235 x 21 mm

Greutate: 0.53 kg

Ediția:2002

Editura: Springer Us

Colecția Springer

Seria Frontiers in Electronic Testing

Locul publicării:New York, NY, United States

ISBN-10: 1402071191

Pagini: 232

Ilustrații: XII, 232 p.

Dimensiuni: 155 x 235 x 21 mm

Greutate: 0.53 kg

Ediția:2002

Editura: Springer Us

Colecția Springer

Seria Frontiers in Electronic Testing

Locul publicării:New York, NY, United States

Public țintă

ResearchCuprins

1. Test Resource Partitioning.- 2. Test Access Mechanism Optimization.- 3. Improved Test Bus Partitioning.- 4. Test Wrapper And TAM Co-Optimization.- 5. Test Scheduling.- 6. Precedence, Preemption, And Power Constraints.- 7. Test Data Compression Using Golomb Codes.- 8. Frequency-Directed Run-Length (FDR) Codes.- 9. TRP for Low-Power Scan Testing.- 10. Conclusion.- References.